Feb 14 2013

RFEL, who specialises in high performance, electronic signal processing solutions, now has available its Video Image Stabilisation IP Core, which is the first of its recently announced family of Video Processing IP cores that fully utilises the power of the Xilinx Zynq-7000 All Programmable SoCs.

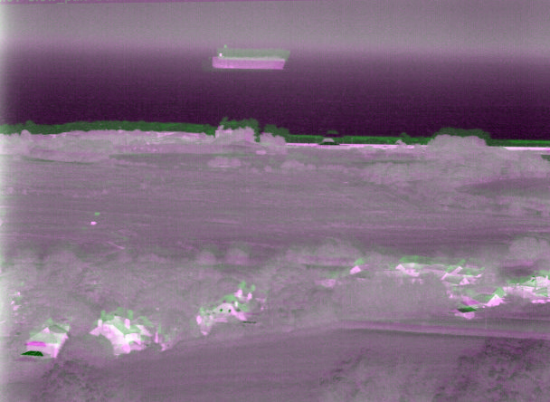

Unstabilised image set. The 5 frames have been false-coloured and superimposed to illustrate the movement effect.

Unstabilised image set. The 5 frames have been false-coloured and superimposed to illustrate the movement effect.

Stabilisation is performed in real-time and entirely digitally, with the algorithm compensating for unwanted roll and horizontal and vertical shifts of a scene, thereby improving the display to the end-user and reducing work-load. The IP core can be configured to be highly resource efficient and very low power if required.

"Image stabilisation is an important capability for many electro-optic sensors," explained Dr Alex Kuhrt, CEO of RFEL Ltd. "Our IP-Core can therefore enhance many practical viewing systems, spanning a very broad range of applications including those found in defence and security sectors. The Image Stabilisation IP-Core provides a means for reducing both image blur and unwanted frame-to-frame image shifts and rotations, thereby aiding image interpretation and reducing the operator's workload."

While current electronic image stabilisation approaches use prominent image features to generate frame-to-frame flow vectors, and relatively simple processing in order to achieve sufficient throughput performance, RFEL's approach is to process image frames on a tiled basis in the spatial frequency domain. This allows the IP Core to process all of the scene information and gives a far more robust and accurate stabilisation solution.

RFEL's new Stabilisation IP Core is a high-performance video processing system that can readily support high input resolutions and frame rates, while maintaining low latency and power consumption. "We designed the IP-Core to be compatible with cameras that operate over different spectral bands and to be rapidly integrated into third-party hardware," Alex Kuhrt added.

The Stabilisation Core is designed to deliver a stable image under the most demanding of applications, including: driving aids for military vehicles, diverse airborne platforms, targeting systems and remote border security cameras. The algorithm implemented within the IP core stabilises images subjected to two-dimensional translations and rotations, from both static and moving platforms. The stabilisation function provides real-time correction at frame-rates of up to 150 Hz for various imaging devices, or for resolutions of up to 1080p including both daylight and infrared cameras. For example, a 1080p colour camera operating at 8 bits and with a frame-rate of 60 Hz, necessitates operation with an input data rate of ~1 Gbits/s. The accuracy of image stabilisation, achieved when tested using a very diverse and demanding range of evaluation video data, has been shown to be better than ±1 pixels, even when subjected to random frame-to frame displacements of up to ±25 pixels in the x and y directions and with a frame-to-frame rotational variation of up to ±5°.

The Image Stabilisation IP-Core is designed to work on all suitable major FPGA vendors' devices, although additional performance is available for Xilinx Zynq-7000 SoC devices only.